**A RIGOROUS STUDY OF WIRE-BONDING AND VIA-HOLE EFFECTS

ON GaAs FIELD EFFECT TRANSISTORS<sup>†</sup>**

Tzyy-Sheng Horng

Electrical Engineering Department, National Sun Yat-Sen University, Kaohsiung, Taiwan 80424, R.O.C.

<sup>†</sup> This research was supported by the National Science Council, R.O.C., under grant NSC84-2221-E-110-005.

**Abstract**

A new procedure is presented for evaluation of the wire-bonding and via-hole effects on a GaAs FET at microwave frequencies. The analysis not only provides a rigorous characterization of the passive elements, like bond-wires, via-holes and microstrips, on a GaAs FET but also includes their mutual coupling with the active region. For practical applications, the corresponding gate, source and drain inductances, which are the important extrinsic parameters of a CAD oriented equivalent circuit model, are extracted based on the calculated S parameters.

**I. Introduction**

It is a well known property that the variations of the gain and noise figure parameters of a GaAs FET due to bond-wires and via-holes become more evident at higher microwave frequencies. Provision of accurate characterization data representing the effects of such elements is therefore of primary importance for every GaAs FET manufacturer. Generally speaking, the most commonly used small-signal equivalent circuit model for a GaAs FET can be divided into two parts: the intrinsic parameters and the extrinsic parameters. The intrinsic parameters characterize the active region and are functions of biasing conditions, whereas the extrinsic parameters result from the passive elements and depend on the geometrical parameters of bond-wires, via-holes, microstrips, substrates etc.

Numerous approaches for direct extraction of the intrinsic and extrinsic parameters from measured S-parameter data has been discussed since years [1]-[3]. To achieve the best results for extrinsic parameters, the FET should be measured in the medium in which it will be used. However, the actual measurement of the S parameters is made in a test fixture using a network analyzer. The style of the fixture will greatly influence the measurement. Recently, the full-wave numerical techniques make rapid progress in analyzing the three-dimensional metallization structures in a layered medium. Accurate investigation of bond-wires and via-holes

connected to microstrip lines has been demonstrated. [4],[5] It is observed that these passive elements were studied in an isolated situation. The application to FET models is of limited value since it does not account for the mutual coupling among the passive elements as well as the active region of a FET.

In this analysis, the metallization parts of a FET are replaced by current density distribution, whereas the active region is represented by a widely used 10-element equivalent circuit model. To satisfy the boundary conditions on the metallization structure and the I-V characteristics of the active region obtained from the equivalent circuit model, an electric-field integral equation can be derived. An iterative method of moments is then developed to solve the integral equation and find the current distribution on microstrip lines, and subsequently the S parameters and the equivalent gate, source and drain inductances.

**II. Theory**

**1. The Equivalent Circuit of the Active Region**

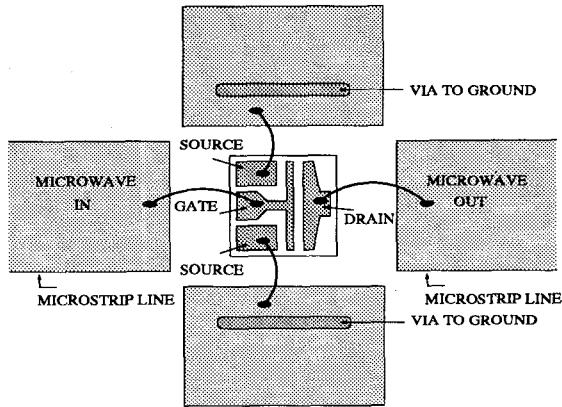

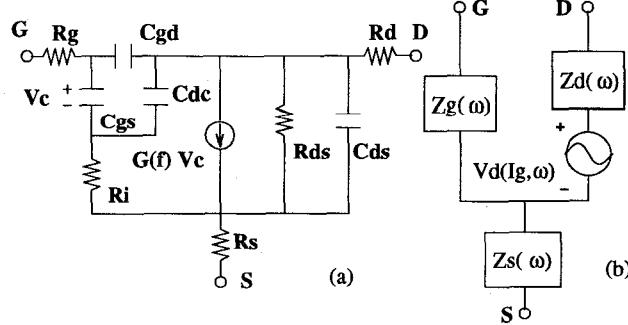

Fig. 1 shows a typical common source configuration for a GaAs FET. For this structure to function as an amplifier, proper bias conditions needs to be established. This determines the values of intrinsic parameters of a small-signal equivalent circuit as illustrated in Fig. 2(a). To derive the electric-field integral equation associated with the FET conveniently, the circuit is simplified as that in Fig. 2(b) in which the expressions of circuit elements are given as

$$Z_g(\omega) = R_g + \frac{1}{j\omega C_{gs}} + R_i - \frac{T_g(\omega)}{T_n(\omega)}, \quad (1)$$

$$Z_d(\omega) = R_d + Z_{ds}(\omega) - \frac{T_d(\omega)}{T_n(\omega)}, \quad (2)$$

$$Z_s(\omega) = R_s + \frac{T_s(\omega)}{T_n(\omega)}, \quad (3)$$

$$V_e(I_g, \omega) = I_g \frac{T_e(\omega)}{T_n(\omega)} \quad (4)$$

WE

3F

where

$$\begin{aligned}

T_g(\omega) &= (R_i^2 + R_i Z_{ds}(\omega)) \left( \frac{1}{C_{gd}} + \frac{1}{C_{dc}} + \frac{1}{C_{gs}} \right) \\

&+ \frac{G(\omega) Z_{ds}(\omega) R_i}{j\omega C_{gs} C_{gd}} + \frac{R_i + Z_{ds}(\omega)}{j\omega C_{gs}^2} \\

&+ \frac{1}{j\omega C_{gs} C_{dc}} (2R_i + Z_{ds}(\omega)) \\

&+ G(\omega) Z_{ds}(\omega) R_i + \frac{1 + G(\omega) Z_{ds}(\omega)}{j\omega C_{gs}}, \quad (5)

\end{aligned}$$

$$\begin{aligned}

T_d(\omega) &= \left( \frac{1}{C_{gd}} + \frac{1}{C_{dc}} + \frac{1}{C_{gs}} \right) (Z_{ds}^2(\omega) + Z_{ds}(\omega) R_i) \\

&+ \frac{Z_{ds}(\omega) + G(\omega) Z_{ds}^2(\omega)}{j\omega C_{dc} C_{gs}}, \quad (6)

\end{aligned}$$

$$T_s(\omega) = Z_{ds}(\omega) R_i \left( \frac{1}{C_{gd}} + \frac{1}{C_{dc}} + \frac{1}{C_{gs}} \right) + \frac{Z_{ds}(\omega)}{j\omega C_{dc} C_{gs}}, \quad (7)$$

$$\begin{aligned}

T_n(\omega) &= \left( \frac{1}{C_{gd}} + \frac{1}{C_{dc}} + \frac{1}{C_{gs}} \right) (R_i + Z_{ds}(\omega)) \\

&+ \frac{1}{C_{dc}} \left( \frac{1 + G(\omega) Z_{ds}(\omega)}{j\omega C_{gs}} + \frac{1}{j\omega C_{gd}} \right), \quad (8)

\end{aligned}$$

$$T_e(\omega) = \frac{G(\omega) Z_{ds}(\omega)}{\omega^2 C_{gs} C_{dc} C_{gd}} - \frac{G(\omega) Z_{ds}(\omega) R_i}{j\omega C_{gs} C_{gd}}, \quad (9)$$

$$Z_{ds}(\omega) = \frac{R_{ds}}{1 + j\omega R_{ds} C_{ds}}, \quad (10)$$

$$G(\omega) = g_m e^{-j\omega\tau} \quad (11)$$

Figure 1: The common source configuration of a GaAs FET.

Figure 2: (a) The small-signal equivalent circuit of a GaAs FET. (b) A simplified circuit of (a).

## 2. Full-Wave Analysis of the Passive Elements

The currents over all the conductors of a FET can be treated as a continuous distribution of Hertzian dipoles. In the Green's function formulation the electric field is written as

$$\vec{E}(x, y, z) = \int_{\text{metal}} \overline{\vec{G}}(x-x', y-y', z-z') \cdot \vec{J}(x', y', z') dx' dy' dz' \quad (12)$$

where  $\overline{\vec{G}}$  is the dyadic Green's function with respect to the GaAs substrate structure and  $\vec{J}$  is the volume current density distributed on the metallization structure. If the perfect conductor is assumed, an electric-field integral equation can be obtained by imposing the boundary condition that the total electric field inside the conductor is zero:

$$\begin{aligned}

\vec{E}(x, y, z) + \vec{E}_{\text{inc}}(x, y, z) + \vec{E}_{\text{act}}(x, y, z) &= 0, \\

\text{for } x, y, z \text{ inside the conductor.} \quad (13)

\end{aligned}$$

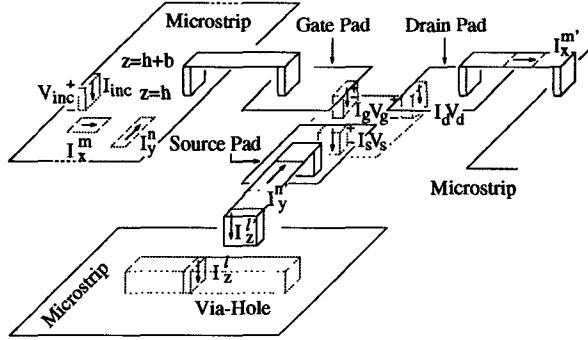

It is noted that  $E_{\text{inc}}$  and  $E_{\text{act}}$  represent an impressed electric field generated at the input end and at the active region, respectively. The method of moments is used to transform (13) into a matrix equation. For simplicity, the bond-wires, via-holes and microstrips of a FET are restricted to a rectangular shape, as shown in Fig. 3. Expanded by pulse and roof-top basis functions, the volume current density is formulated as

$$\begin{aligned}

\vec{J}(x', y', z') &= \hat{x} \sum_m \frac{I_x^m}{d_y} t\left(\frac{x' - x_m}{d_x}\right) p\left(\frac{y' - y_m}{d_y}\right) \delta(z' - h) \\

&+ \hat{x} \sum_{m'} \frac{I_x^{m'}}{d_y} t\left(\frac{x' - x_{m'}}{d_x}\right) p\left(\frac{y' - y_{m'}}{d_y}\right) \delta(z' - h - b) \\

&+ \hat{y} \sum_n \frac{I_y^n}{d_x} p\left(\frac{x' - x_n}{d_x}\right) t\left(\frac{y' - y_n}{d_y}\right) \delta(z' - h) \\

&+ \hat{y} \sum_{n'} \frac{I_y^{n'}}{d_x} p\left(\frac{x' - x_{n'}}{d_x}\right) t\left(\frac{y' - y_{n'}}{d_y}\right) \delta(z' - h - b) \\

&+ \hat{z} \sum_l \frac{I_z^l}{d_x d_y} p\left(\frac{x' - x_l}{d_x}\right) p\left(\frac{y' - y_l}{d_y}\right) p\left(\frac{z' - z_l}{h}\right) \\

&+ \hat{z} \sum_{l'} \frac{I_z^{l'}}{d_x d_y} p\left(\frac{x' - x_{l'}}{d_x}\right) p\left(\frac{y' - y_{l'}}{d_y}\right) p\left(\frac{z' - z_{l'}}{b}\right) \\

&+ \hat{z} \frac{I_{\text{inc}}}{d_x d_y} p\left(\frac{x' - x_i}{d_x}\right) p\left(\frac{y' - y_i}{d_y}\right) p\left(\frac{z' - z_i}{h}\right) \\

&+ \hat{z} \frac{I_g}{d_x d_y} p\left(\frac{x' - x_g}{d_x}\right) p\left(\frac{y' - y_g}{d_y}\right) p\left(\frac{z' - z_g}{d}\right) \\

&+ \hat{z} \frac{I_s}{d_x d_y} p\left(\frac{x' - x_s}{d_x}\right) p\left(\frac{y' - y_s}{d_y}\right) p\left(\frac{z' - z_s}{d}\right) \\

&+ \hat{z} \frac{I_d}{d_x d_y} p\left(\frac{x' - x_d}{d_x}\right) p\left(\frac{y' - y_d}{d_y}\right) p\left(\frac{z' - z_d}{d}\right) \quad (14)

\end{aligned}$$

where

$$t(u) = \begin{cases} 1 - |u|, & |u| \leq 1 \\ 0, & |u| > 1, \end{cases} \quad (15)$$

and

$$p(u) = \begin{cases} 1, & |u| \leq \frac{1}{2} \\ 0, & |u| > \frac{1}{2} \end{cases} \quad (16)$$

Note that  $I_{inc}$  is the incident current excited by a sinusoidal voltage  $V_{inc}$  placed at the input end.  $I_g$ ,  $I_d$  and  $I_s$  represent the current on the gate, source and drain respectively. They have to satisfy the relation:

$$I_g + I_d + I_s = 0. \quad (17)$$

Figure 3: Three-dimensional modeling of a GaAs FET.

### 3. The Matrix Formulation

As suggested in Fig. 3, equation (17) is approximately correct for connecting all the bond-wires to an imaginary patch of sufficiently small size. In the meantime, the patch is assumed to be equipotential such that the voltage drops inside the active region can be approximated as

$$V_g = I_g Z_g(\omega), \quad (18)$$

$$V_s = I_s Z_s(\omega), \quad (19)$$

$$V_d = I_d Z_d(\omega) + V_e(I_g, \omega). \quad (20)$$

With the testing functions chosen to be the same as the expansion functions, the moment method procedure results in a matrix equation in the form

$$\begin{bmatrix} [Z_{I_x I_x}] & [Z_{I_x I_y}] & [Z_{I_x I_z}] \\ [Z_{I_y I_x}] & [Z_{I_y I_y}] & [Z_{I_y I_z}] \\ [Z_{I_z I_x}] & [Z_{I_z I_y}] & [Z_{I_z I_z}] \end{bmatrix} \begin{bmatrix} [I_x] \\ [I_y] \\ I_z^1 \\ \vdots \\ \vdots \\ \vdots \\ I_{inc} \\ \vdots \\ \vdots \\ \vdots \\ I_g \\ I_s \\ I_d \end{bmatrix} = \begin{bmatrix} [0] \\ [0] \\ 0 \\ \vdots \\ 0 \\ 0 \\ V_{inc} \\ \vdots \\ \vdots \\ 0 \\ V_g \\ V_s \\ V_d \end{bmatrix}. \quad (21)$$

The computation of each reaction element  $Z_{I_u I_v}$  in the left-hand side matrix can be performed using a spectral-domain approach [6]. Substituting (18) ~ (20) into (21), one will find that the right-hand side column matrix contains the

unknown current coefficients which are not removable. Under this situation, an iterative scheme will be required to solve for the coefficients [7]. The S parameters are further extracted from knowledge of the current distribution and the propagation constant of the dominant microstrip mode.

## III. Numerical Results

### 1. The Common Source Configuration

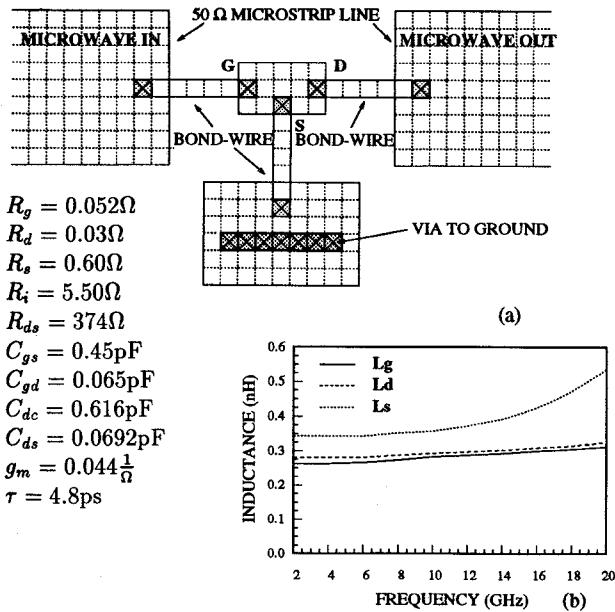

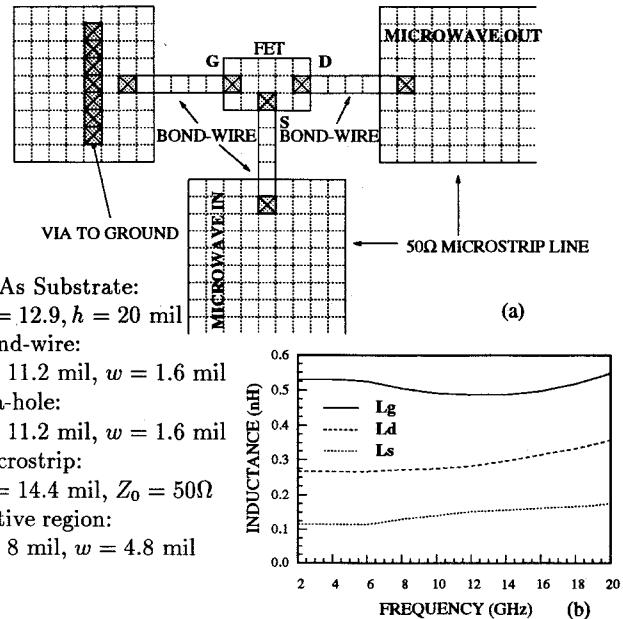

Fig. 4(a) shows the layout of a common source configuration. With the calculated results of the S parameters, one can approximate the values of the equivalent gate, source and drain inductances using the following expressions:

$$L_g \simeq \frac{Z_0 (1 + S_{11})(1 - S_{22}) + S_{12}S_{21} - 2S_{12}}{j\omega (1 - S_{11})(1 - S_{22}) - S_{12}S_{21}} - \frac{Z_g(\omega)}{j\omega}, \quad (22)$$

$$L_s \simeq \frac{Z_0 2S_{12}}{j\omega (1 - S_{11})(1 - S_{22}) - S_{12}S_{21}} - \frac{Z_s(\omega)}{j\omega}, \quad (23)$$

$$L_d \simeq \frac{Z_0 (1 - S_{11})(1 + S_{22}) + S_{12}S_{21} - 2S_{12}}{j\omega (1 - S_{11})(1 - S_{22}) - S_{12}S_{21}} - \frac{Z_d(\omega)}{j\omega} \quad (24)$$

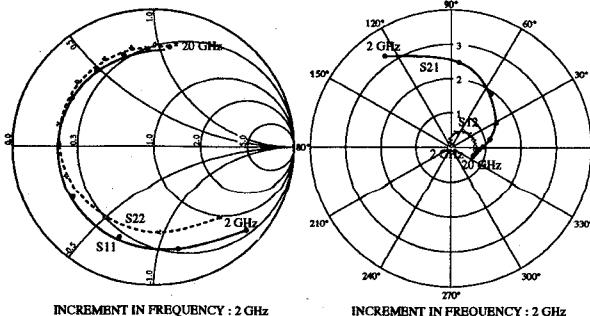

where  $Z_0$  is the characteristic impedance of the microstrip line. The results of equivalent inductances are shown in Fig. 4(b). For a self-consistency check, the S parameters are compared with those calculated from the equivalent circuit model, as plotted in Fig. 5. Good agreement is observed over a wide frequency range.

### 2. The Common Gate Configuration

Fig. 6(a) shows the layout of a common gate configuration. The corresponding equivalent inductances can be approximated as

$$L_g \simeq \frac{Z_0 2S_{12}}{j\omega (1 - S_{11})(1 - S_{22}) - S_{12}S_{21}} - \frac{Z_g(\omega)}{j\omega}, \quad (25)$$

$$L_s \simeq \frac{Z_0 (1 + S_{11})(1 - S_{22}) + S_{12}S_{21} - 2S_{12}}{j\omega (1 - S_{11})(1 - S_{22}) - S_{12}S_{21}} - \frac{Z_s(\omega)}{j\omega}, \quad (26)$$

$$L_d \simeq \frac{Z_0 (1 - S_{11})(1 + S_{22}) + S_{12}S_{21} - 2S_{12}}{j\omega (1 - S_{11})(1 - S_{22}) - S_{12}S_{21}} - \frac{Z_d(\omega)}{j\omega}. \quad (27)$$

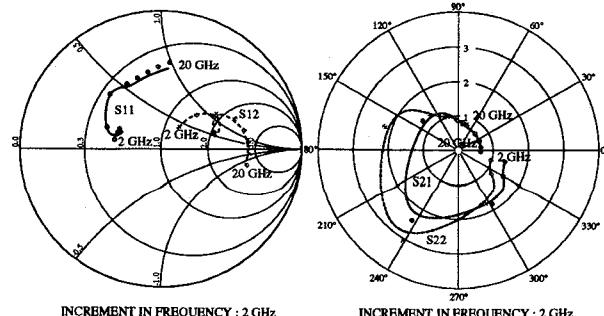

In a similar fashion we plot the results of the inductances and the S parameters in Fig. 6(b) and Fig. 7, respectively.

## IV. Conclusion

A theoretical approach for studying the wire-bonding and via-hole effects on a GaAs FET was given. Through the arrangement of the bond-wire and via-hole locations, the FET has been connected in common source or common gate configuration. The corresponding scattering parameters and the equivalent gate, source and drain inductances were extracted from a full-wave solution of the current distribution on microstrip lines.

## References

- [1] R. Anholt and S. Swirhun, "Equivalent circuit parameter extraction for cold GaAs MESFETs, *IEEE Trans. Microwave Theory Tech.*, vol. 39, pp. 1243-1247, July 1991.

- [2] G. Kompa and M. Novotny, "Highly consistent FET model parameter extraction based on broadband S-parameter measurements, *1992 IEEE MTT-S Digest*, vol. 2, pp. 293-296.

- [3] D. Lovelace, J. Costa and N. Camilleri, "Extracting small-signal model parameters of silicon MOSFET transistors," *1994 IEEE MTT-S Digest*, vol. 2, pp. 865-868.

Figure 4: (a) The layout of a common source configuration. (b) The equivalent gate, source and drain inductances versus frequency.

Figure 5: The comparison of the scattering parameters extracted from the current distribution on the microstrip lines (solid and dashed curves) and calculated from the equivalent circuit model (dark and gray circles) for a common source configuration.

- [4] T. Becks and I. Wolff, "Analysis of 3-D metallization structures by a full-wave spectral-domain technique", *IEEE Trans. Microwave Theory Tech.*, vol. 40, pp. 2219-2227, Dec. 1992.

- [5] R. Sorrentino, *et al.* "Full-wave modeling of via hole grounds in microstrip by three-dimensional mode matching technique," *IEEE Trans. Microwave Theory Tech.*, vol. 40, pp. 2228-2234, Dec. 1992.

- [6] M. Tsai, "Via hole modeling for multi-layered microstrip circuits," Master's Thesis, UCLA, 1993.

- [7] T.S. Horng, "Extending the three-dimensional spectral-domain approach to hybrid microwave integrated circuits with passive and active lumped elements," *1994 IEEE MTT-S Digest*, vol. 3, pp. 1777-1780.

Figure 6: (a) The layout of a common gate configuration. (b) The equivalent gate, source and drain inductances versus frequency.

Figure 7: The comparison of the scattering parameters extracted from the current distribution on the microstrip lines (solid and dashed curves) and calculated from the equivalent circuit model (dark and gray circles) for a common gate configuration.